Finalizada la 1a fase para el procesador HPC europeo

hace 2 años

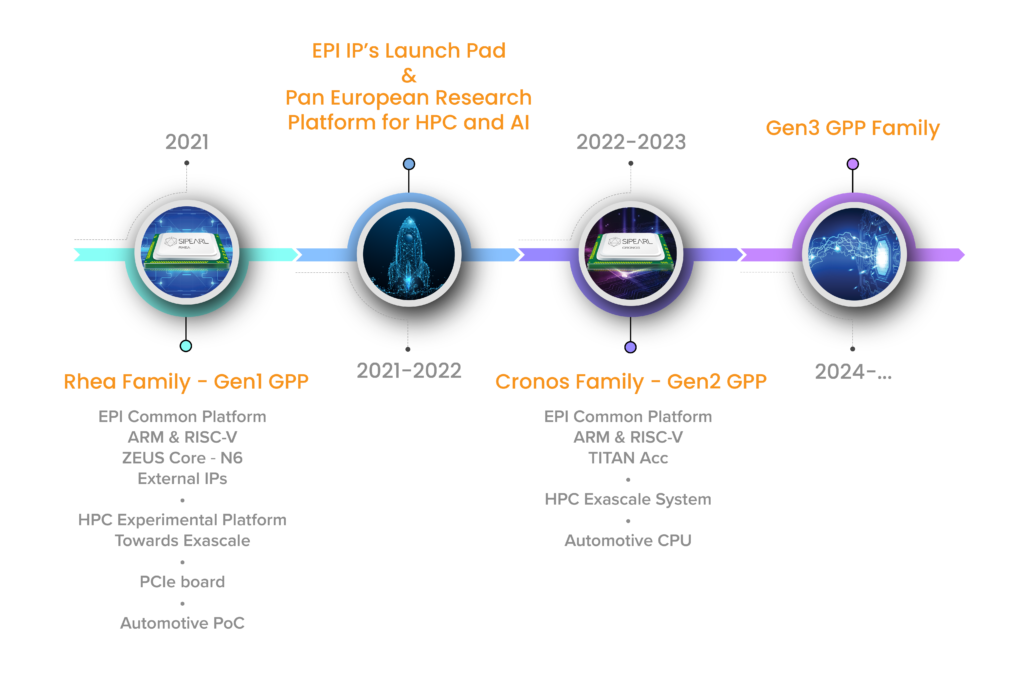

La European Processor Initiative, que reúne a 28 actores tecnológicos de la UE para diseñar un procesador HPC europeo, presentó sus primeros resultados. Además de las especificaciones arquitectónicas del Rhea, la 1ª generación del procesador universal para el EPI, el proyecto llevó a cabo una prueba de concepto para un acelerador y un microcontrolador de a bordo de alto rendimiento para aplicaciones de automoción.

El mundo de la informática de alto rendimiento está desarrollando un procesador europeo que permita a la UE ganar independencia en tecnologías de chips e infraestructura para superordenadores de exaescala. Lanzada en 2018, la European Processor Initiative (EPI) reúne a un consorcio de 28 socios de 10 países

. El proyecto acaba de completar una primera fase de tres años y los resultados obtenidos se comunicaron la semana pasada en los tres principales campos de investigación explorados: un procesador universal (GPP), aceleradores FPGA y aplicaciones en la industria automotriz.

El fabricante francés Atos / Bull está pilotando el primer campo de investigación con la empresa franco-alemana SiPearl. Juntos, definieron las especificaciones arquitectónicas del microprocesador Rhea de alto rendimiento y bajo consumo para la supercomputadora de exaescala europea. "Con 29 núcleos Risc-V, la arquitectura Arm Neoverse V1 utilizada por SiPearl para diseñar el Rhea proporcionará una solución eficiente, escalable y personalizable para aplicaciones HPC", dijo el EPI en su comunicado de prensa. El consorcio cree que los resultados obtenidos en esta primera fase del proyecto serán decisivos para el lanzamiento de las supercomputadoras exascales europeas en 2023.

La primera generación de chip HPC desarrollado por la European Processor Initiative combina núcleos Risc-V y la arquitectura Arm Neoverse V1. (Crédito EPI)

Un prototipo virtual del procesador

SiPearl ha optimizado una red en chip (NoC) para transferencias de datos de alta frecuencia y gran ancho de banda entre núcleos, aceleradores, E / S y recursos de memoria compartida. La versión de EPI agrega que se ha diseñado y utilizado un prototipo virtual del procesador para realizar estimaciones de rendimiento y desarrollos de software muy tempranos. Grabado en 6 nm en TSMC, el procesador Rhea integrará las tecnologías de los socios del proyecto EPI en arquitectura de memoria, optimización del ancho de banda, seguridad y gestión del consumo de energía. Con respecto a la memoria, para ayudar a evaluar las opciones arquitectónicas, el CEA ha desarrollado una plataforma de simulación para analizar la eficiencia del controlador en la conducción de memorias de alto ancho de banda HBM2E. En las funciones de seguridad integradas, ProvenRun trae su tecnología de gestión de seguridad independiente para HPC y procesadores de borde, y la Universidad de Pisa su tecnología Crypto Tile. Este último incluye un módulo hardware para cifrado simétrico (AES con 9 modos de cifrado), asimétrico (ECC, ECDSA, ECIES, ECDH) y hash (SHA2 / SHA3). El EPI especifica que este módulo ofrece varios órdenes de magnitud para aumentar el ancho de banda y reducir el consumo en comparación con una solución de software. Crypto Tile también incluye configuración y almacenamiento seguro de claves, protección contra ataques de canal lateral y generación de números aleatorios en el chip (TRNG), entre otros. El soporte para el cifrado post-cuántico lo proporciona la implementación de algoritmos como Kyber y Dilithium. En el campo del consumo de energía, la Universidad de Bolonia y ETH Zurich diseñaron un controlador de código abierto basado en una arquitectura Risc-V e integrado en el procesador Rhea. Aprovecha los algoritmos de IA para la gestión de energía SoC a gran escala. Además, AtoS y E4 Computer Engineering han desarrollado una plataforma de prueba de gestión de energía de referencia basada en componentes de STMicroelectronics. Al final de esta primera fase de 3 años, el proyecto del procesador EPI alcanzó un nivel de finalización RTL (nivel de transferencia de registros, descripción de arquitecturas microelectrónicas), indica el consorcio. El diseño se encuentra en etapa de validación mediante emulaciones.

Aceleración energéticamente eficiente para HPC e IA El consorcio europeo también está trabajando en un acelerador informático, EPAC (aceleradores de procesadores europeos), que es energéticamente eficiente para cargas de trabajo HPC e IA. Él cree que con la prueba de viabilidad realizada en el EPAC, pudo demostrar que era posible crear un diseño exclusivamente europeo, apoyándose en una arquitectura de conjunto de instrucciones de código abierto. EPAC combina varias tecnologías de aceleración especializadas para diferentes aplicaciones. En este trabajo participan SemiDynamics, el Barcelona ComputingCenter y la Universidad de Zagreb, así como Chalmers, Forth, Fraunhofer, ETH Zürich y CEA.

Finalmente, el tercer campo de desarrollo de la iniciativa europea se refiere al sector de la automoción. En esta área, el proyecto EPI ha desarrollado una prueba de concepto para una plataforma informática de alto rendimiento integrada (eHPC) y un SDK asociado. Infineon coordina estos desarrollos. Un logro principal se demostró en un BMW X5, en un PoC de una unidad de microcontrolador eHPC integrada en una plataforma modular que integra varias tecnologías del consorcio EPI. Se llevaron a cabo varias pruebas para recopilar datos y evaluar escenarios de prueba que involucran parámetros de conducción autónoma. Eric Monchalin (Atos), presidente del Consejo de Administración de EPI, destaca los resultados excepcionales obtenidos por los equipos de proyectos europeos tras estos tres años de cooperación.

Los objetivos se alcanzaron a tiempo con un presupuesto limitado, a pesar de las condiciones laborales impuestas por la pandemia. "Esto creó condiciones favorables para el lanzamiento de la siguiente fase y para la entrega de procesadores y aceleradores europeos para los proyectos EUPEX (piloto europeo de exaescala) y TEP (piloto europeo), los precursores de los sistemas de exaescala europeos", escribe. .

Miembros del consorcio EPI: Atos, BSC (centro de supercomputación de Barcelona), Infineon, Semidynamics, CEA, Chalmers, ETHZürich, Forth, Genci, Técnico Lisboa, el centro de investigación Juliers (Jülich Forschungszentrum), Alma Mater Studiorum (Universidad de Bolonia), Facultad de ingeniería eléctrica e informática (Universidad de Zagreb), Fraunhofer, ST Microelectronics, E4 Ingeniería informática, Universidad de Pisa, Surf Sara, Kalray, Extoll, Cineca, BMW Group, Elektrobit, ProveRun, Karlsruher Institut für Technologie, Menta, SiPearl y Kernkonzept.

Si quieres conocer otros artículos parecidos a Finalizada la 1a fase para el procesador HPC europeo puedes visitar la categoría Otros.

Otras noticias que te pueden interesar